# 2.6-W STEREO AUDIO POWER AMPLIFIER WITH FOUR SELECTABLE GAIN SETTINGS

### FEATURES

- Compatible With PC 99 Desktop Line-Out Into 10-kΩ Load

- Internal Gain Control, Which Eliminates External Gain-Setting Resistors

- 2.6-W/Ch Output Power Into 3- $\Omega$  Load

- PC-Beep Input

- Depop Circuitry

- Stereo Input MUX

- Fully Differential Input

- Low Supply Current and Shutdown Current

- Surface-Mount Power Packaging 24-Pin TSSOP PowerPAD™

# DESCRIPTION

The TPA0112 is a stereo audio power amplifier in a 24-pin TSSOP thermally enhanced package capable of delivering 2.6 W of continuous RMS power per channel into  $3-\Omega$  loads. This device minimizes the number of external components needed, simplifying the design, and freeing up board space for other features. When driving 1 W into 8- $\Omega$  speakers, the TPA0112 has less than 0.8% THD+N across its specified frequency range.

Included within this device is integrated depop circuitry that virtually eliminates transients that cause noise in the speakers.

Amplifier gain is internally configured and controlled by way of two terminals (GAIN0 and GAIN1). BTL gain settings of 2, 6, 12, and 24 V/V are provided, while SE gain is always configured as 1 V/V for headphone drive. An internal input MUX allows two sets of stereo inputs to the amplifier. In notebook applications, where internal speakers are driven as BTL and the line outputs (often headphone drive) are required to be SE, the TPA0112 automatically switches into SE mode when the SE/BTL input is activated, and this reduces the gain to 1 V/V.

The TPA0112 consumes only 6 mA of supply current during normal operation. A miserly shutdown mode reduces the supply current to less than 150  $\mu$ A.

The PowerPAD package (PWP) delivers a level of thermal performance that was previously achievable only in TO-220-type packages. Thermal impedances of approximately  $35^{\circ}$ C/W are readily realized in multilayer PCB applications. This allows the TPA0112 to operate at full power into 8- $\Omega$  loads at an ambient temperature of 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

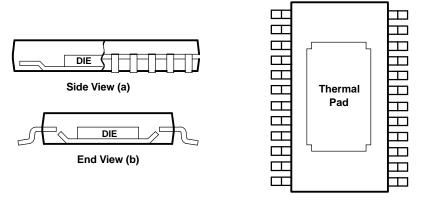

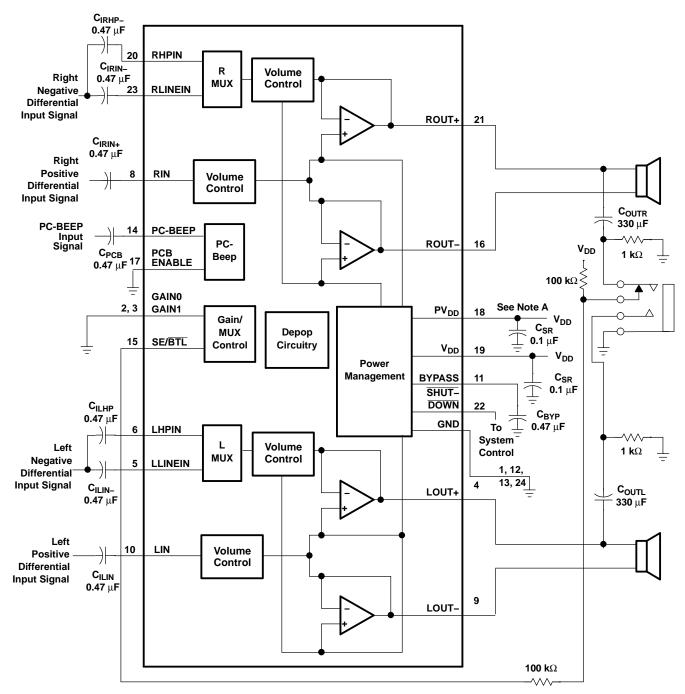

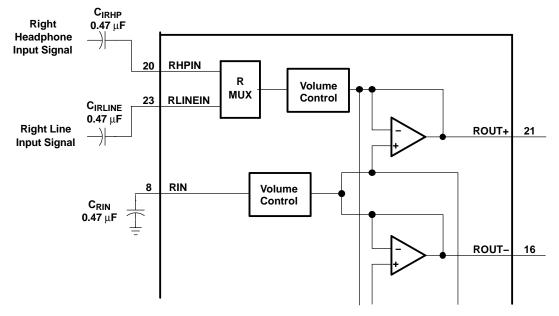

FUNCTIONAL BLOCK DIAGRAM RHPIN · R Volume MUX Control RLINEIN GAIN0 ROUT+ GAIN1 Volume RIN Control ROUT-PC-BEEP -PC Beep PCB ENABLE -MUX  $PV_{DD}$ SE/BTL V<sub>DD</sub> BYPASS Depop Power Control Circuitry Management SHUTDOWN LHPIN L Volume GND MUX LLINEIN Control LOUT+ Volume LIN -Control - LOUT-

These devices have limited built-in ESD protection. The leads should be shorted together or the device

placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **AVAILABLE OPTIONS**

| T <sub>A</sub> | PACKAGED DEVICE            |

|----------------|----------------------------|

|                | TSSOP <sup>(1)</sup> (PWP) |

| –40°C to 85°C  | TPA0112PWP                 |

The PWP package is available taped and reeled. To order a taped and reeled part, add the suffix R to the part number (e.g., TPA0112PWPR).

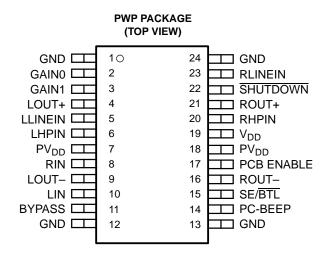

#### **TERMINAL FUNCTIONS**

| TERMINAL         |                  |     |                                                                                                                                                                                                                                   |  |  |

|------------------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME             | NO.              | I/O | DESCRIPTION                                                                                                                                                                                                                       |  |  |

| BYPASS           | 11               |     | Tap to voltage divider for internal mid-supply bias generator                                                                                                                                                                     |  |  |

| GAIN0            | 2                | I   | Bit 0 of gain control                                                                                                                                                                                                             |  |  |

| GAIN1            | 3                | I   | Bit 1 of gain control                                                                                                                                                                                                             |  |  |

| GND              | 1, 12, 13,<br>24 |     | Ground connection for circuitry. Connected to the thermal pad.                                                                                                                                                                    |  |  |

| LHPIN            | 6                | I   | Left channel headphone input, selected when SE/BTL is held high                                                                                                                                                                   |  |  |

| LIN              | 10               | I   | Common left input for fully differential input. AC ground for single-ended inputs.                                                                                                                                                |  |  |

| LLINEIN          | 5                | I   | Left channel line input, selected when SE/BTL is held low                                                                                                                                                                         |  |  |

| LOUT+            | 4                | 0   | Left channel positive output in BTL mode and positive output in SE mode                                                                                                                                                           |  |  |

| LOUT-            | 9                | 0   | Left channel negative output in BTL mode and high impedance in SE mode                                                                                                                                                            |  |  |

| PC-BEEP          | 14               | Ι   | The input for PC Beep mode. PC-BEEP is enabled when a > 1.5-V (peak-to-peak) square wave is input to PC-BEEP or PCB ENABLE is high.                                                                                               |  |  |

| PCB ENABLE       | 17               | I   | If this terminal is high, the detection circuitry for PC-BEEP is overridden and passes PC-BEEP through the amplifier, regardless of its amplitude. If PCB ENABLE is floating or low, the amplifier continues to operate normally. |  |  |

| PV <sub>DD</sub> | 7, 18            | I   | Power supply for output stage                                                                                                                                                                                                     |  |  |

| RHPIN            | 20               | I   | Right channel headphone input, selected when SE/BTL is held high                                                                                                                                                                  |  |  |

| RIN              | 8                | I   | Common right input for fully differential input. AC ground for single-ended inputs.                                                                                                                                               |  |  |

| RLINEIN          | 23               | I   | Right channel line input, selected when SE/BTL is held low                                                                                                                                                                        |  |  |

| ROUT+            | 21               | 0   | Right channel positive output in BTL mode and positive output in SE mode                                                                                                                                                          |  |  |

| ROUT-            | 16               | 0   | Right channel negative output in BTL mode and high-impedance in SE mode                                                                                                                                                           |  |  |

| SHUTDOWN         | 22               | I   | Places entire IC in shutdown mode when held low, except PC-BEEP remains active                                                                                                                                                    |  |  |

| SE/BTL           | 15               | I   | Input MUX control input. When this terminal is held high, the LHPIN or RHPIN and SE output is selected. When this terminal is held low, the LLINEIN or RLINEIN and BTL output are selected.                                       |  |  |

| V <sub>DD</sub>  | 19               | Ι   | Analog $V_{\text{DD}}$ input supply. This terminal needs to be isolated from $\text{PV}_{\text{DD}}$ to achieve highest performance.                                                                                              |  |  |

| Thermal pad      |                  |     | Connect to ground. Must be soldered down in all applications to properly secure the device on the PC board.                                                                                                                       |  |  |

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

| V <sub>DD</sub>  | Supply voltage                                               | 6 V                                               |

|------------------|--------------------------------------------------------------|---------------------------------------------------|

| VI               | Input voltage                                                | –0.3 V to V <sub>DD</sub> +0.3 V                  |

|                  | Continuous total power dissipation                           | Internally Limited (see Dissipation Rating Table) |

| T <sub>A</sub>   | Operating free-air temperature range                         | -40°C to 85°C                                     |

| TJ               | Operating junction temperature range                         | –40°C to 150°C                                    |

| T <sub>stg</sub> | Storage temperature range                                    | –65°C to 85°C                                     |

|                  | Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260°C                                             |

(1) Stresses beyond thoselisted under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at theseor any other conditions beyond those indicated under recommended operatingconditions is not implied. Exposure to absolute-maximum-rated conditions forextended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>A</sub> ≤ 25°C | DERATING FACTOR | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|---------|-----------------------|-----------------|-----------------------|-----------------------|

| PWP     | 2.7 W <sup>(1)</sup>  | 21.8 mW/°C      | 1.7 W                 | 1.4 W                 |

(1) Please see the Texas Instrumentsdocument, PowerPAD Thermally EnhancedPackage Application Report (literature number SLMA002), for moreinformation on the PowerPAD package. The thermal data was measured on a PCBlayout based on the information in the section entitled Texas Instruments Recommended Board forPowerPAD of the before-mentioned document.

#### **RECOMMENDED OPERATING CONDITIONS**

|                 |                                          |                      | MIN                   | MAX                          | UNIT |  |

|-----------------|------------------------------------------|----------------------|-----------------------|------------------------------|------|--|

| V <sub>DD</sub> | Supply voltage                           |                      | 4.5                   | 5.5                          | V    |  |

|                 | High lovel input veltage                 | SE/BTL, GAIN0, GAIN1 | 0.8 x V <sub>DD</sub> |                              |      |  |

| vн              | V <sub>IH</sub> High-level input voltage | SHUTDOWN             | 2                     |                              | v    |  |

|                 |                                          | SE/BTL               |                       | $0.6 \times V_{DD}$          |      |  |

| V <sub>IL</sub> | V <sub>IL</sub> Low-level input voltage  | GAIN0, GAIN1         |                       | $0.4 	ext{ x V}_{\text{DD}}$ | V    |  |

|                 |                                          | SHUTDOWN             |                       | 0.8                          |      |  |

| T <sub>A</sub>  | Operating free-air temperature           |                      | -40                   | 85                           | °C   |  |

### **ELECTRICAL CHARACTERISTICS**

at specified free-air temperature,  $V_{DD}$  = 5 V,  $T_A$  = 25°C (unless otherwise noted)

|                     | PARAMETER                                       | TEST CONDITIONS                    | MIN TYP | MAX | UNIT |

|---------------------|-------------------------------------------------|------------------------------------|---------|-----|------|

| V <sub>oo</sub>     | Output offset voltage (measured differentially) | $V_1 = 0, A_V = 2 V/V$             |         | 25  | mV   |

| PSRR                | Power supply rejection ratio                    | $V_{DD} = 4.5 V \text{ to } 5.5 V$ | 77      |     | dB   |

| I <sub>IH</sub>     | High-level input current                        | $V_{DD} = 5.5 V, V_I = V_{DD}$     |         | 900 | nA   |

| I <sub>IL</sub>     | Low-level input current                         | $V_{DD} = 5.5 V, V_1 = 0 V$        |         | 900 | nA   |

|                     | Supply ourront                                  | BTL mode                           | 6       | 8   | mA   |

| DD                  | Supply current                                  | SE mode                            | 3       | 4   | IIIA |

| I <sub>DD(SD)</sub> | Supply current, shutdown mode                   |                                    | 150     | 300 | μA   |

### **OPERATING CHARACTERISTICS**

$V_{\text{DD}}$  = 5 V,  $T_{\text{A}}$  = 25°C,  $R_{\text{L}}$  = 8  $\Omega$  , Gain = 2 V/V, BTL mode

| PARAMETER       |                                      | TEST CC                                                                | TEST CONDITIONS     |       | MAX | UNIT              |

|-----------------|--------------------------------------|------------------------------------------------------------------------|---------------------|-------|-----|-------------------|

|                 | $P_0$ Output power $R_L = 3 \Omega$  | P = 2 0                                                                | THD+N = 10%         | 2.6   |     | W                 |

| F0              |                                      | $R_{L} = 5.52$                                                         | THD+N = 1%          | 2.05  |     | vv                |

| THD + N         | Total harmonic distortion plus noise | P <sub>O</sub> = 1 W,                                                  | f = 20 Hz to 15 kHz | 0.75% |     |                   |

| B <sub>OM</sub> | Maximum output power bandwidth       | THD = 5%                                                               |                     | >15   |     | kHz               |

|                 | Supply ripple rejection ratio        | $\begin{array}{l} f=1 \text{ kHz},\\ C_B=0.47 \mu\text{F} \end{array}$ | BTL mode            | -72   |     | dB                |

| SNR             | Signal-to-noise ratio                |                                                                        |                     | 105   |     | dB                |

| V               | C <sub>B</sub>                       | C <sub>B</sub> = 0.47 μF,                                              | BTL mode            | 20    |     |                   |

| V <sub>n</sub>  | Noise output voltage                 | f = 20 Hz to 20 kHz                                                    | SE mode             | 18    |     | μV <sub>RMS</sub> |

| ZI              | Input impedance <sup>(1)</sup>       |                                                                        |                     |       |     |                   |

(1) See Table 1 and its associated text.

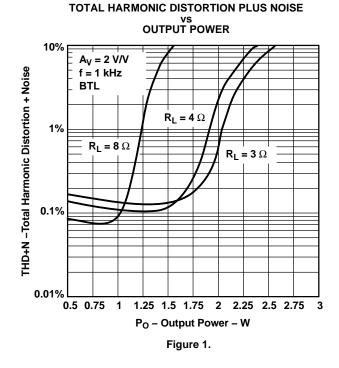

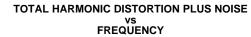

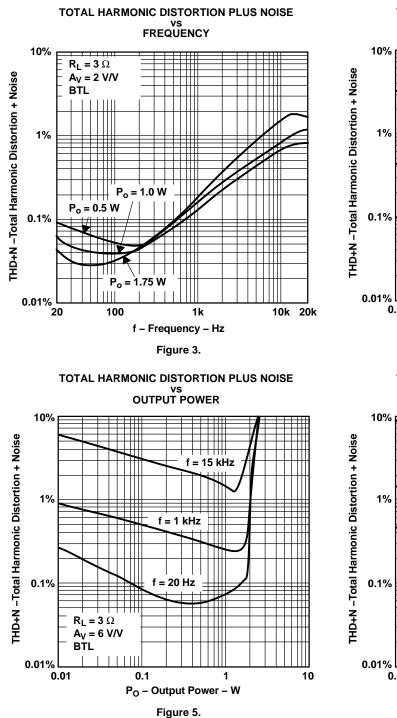

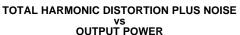

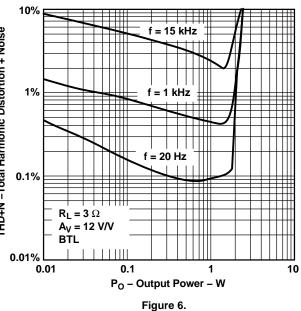

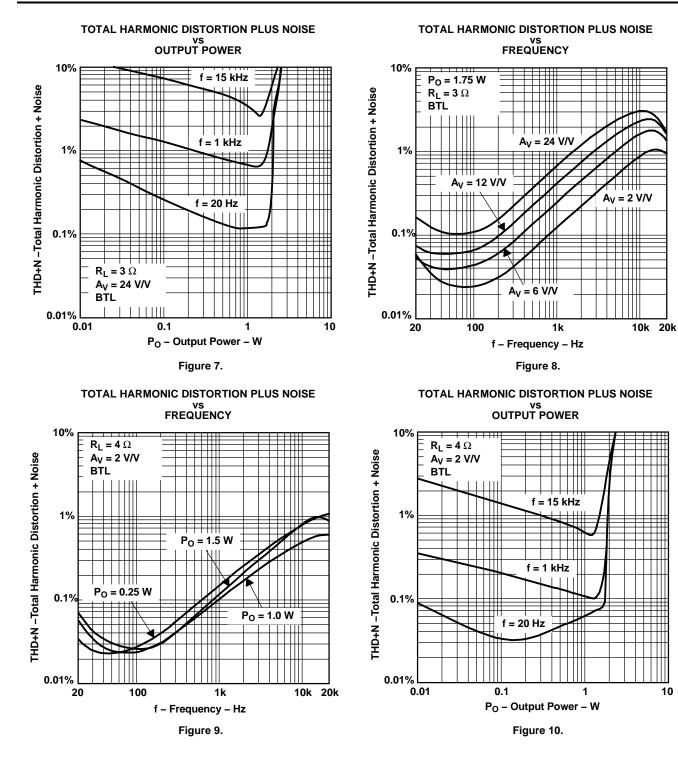

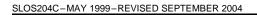

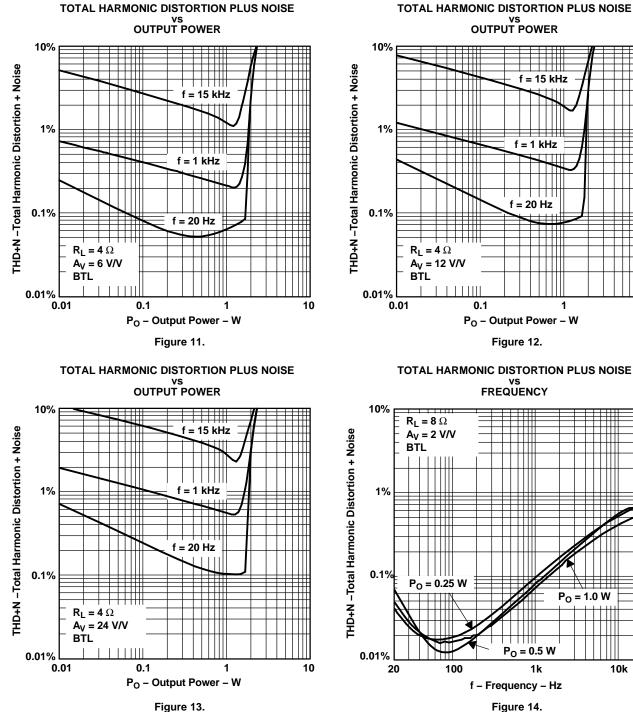

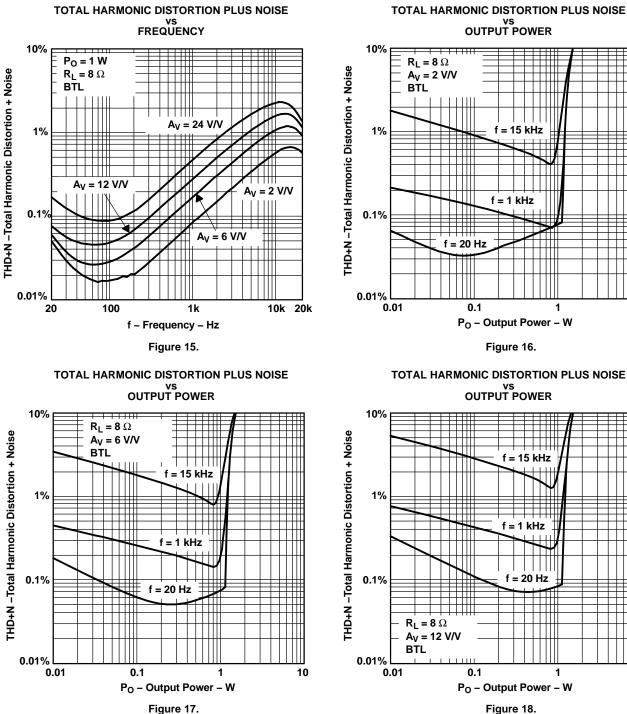

### **TYPICAL CHARACTERISTICS**

| TABLE | OF         | GRAPHS |

|-------|------------|--------|

|       | <b>U</b> . |        |

|                |                                      |                        | FIGURE                        |

|----------------|--------------------------------------|------------------------|-------------------------------|

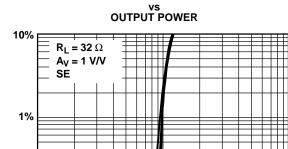

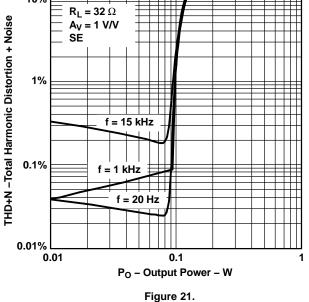

|                |                                      | vs Output power        | 1, 4-7, 10-13,<br>16-19, 21   |

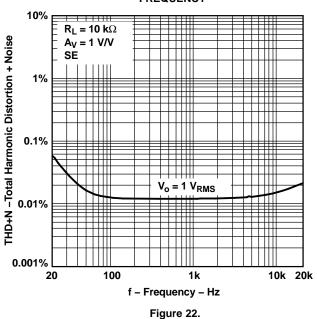

| THD+N          | Total harmonic distortion plus noise | vs Frequency           | 2, 3, 8, 9, 14,<br>15, 20, 22 |

|                |                                      | vs Output voltage      | 23                            |

| V <sub>n</sub> | Output noise voltage                 | vs Bandwidth           | 24                            |

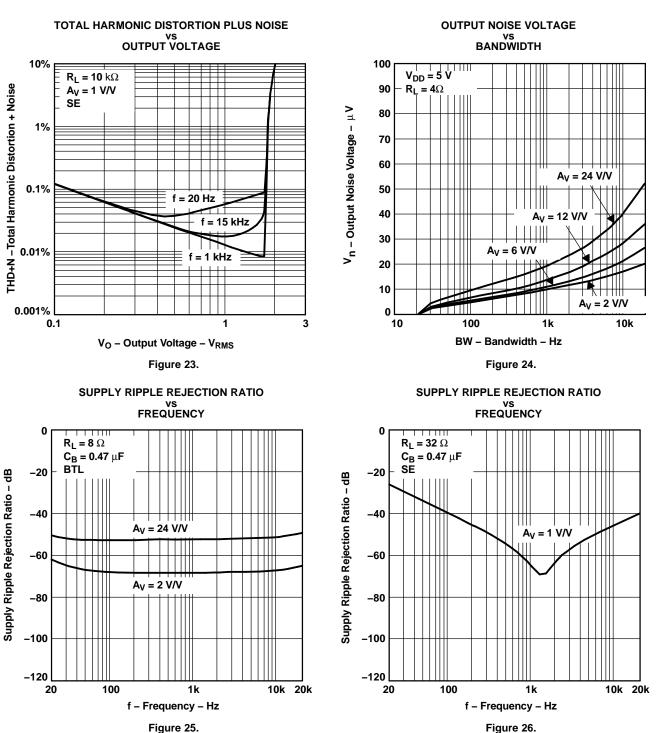

|                | Supply ripple rejection ratio        | vs Frequency           | 25, 26                        |

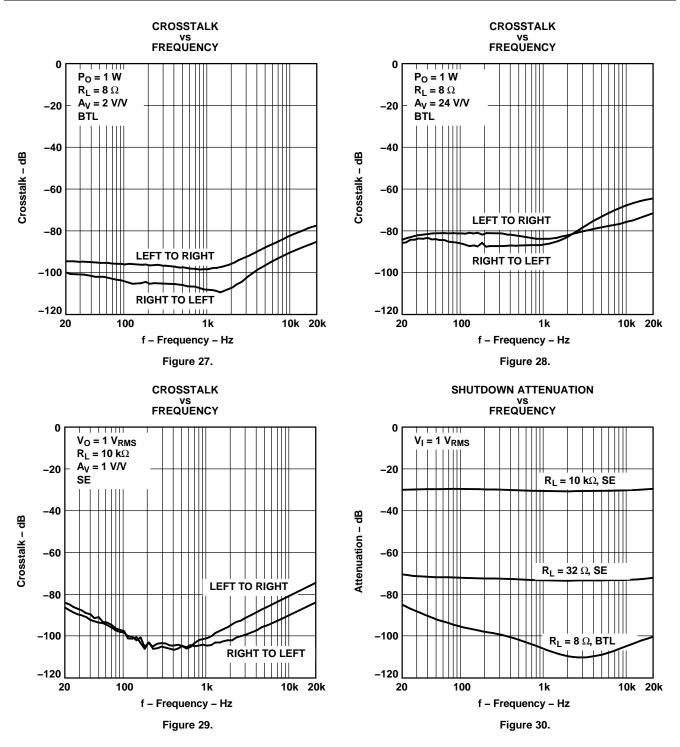

|                | Crosstalk                            | vs Frequency           | 27-29                         |

|                | Shutdown attenuation                 | vs Frequency           | 30                            |

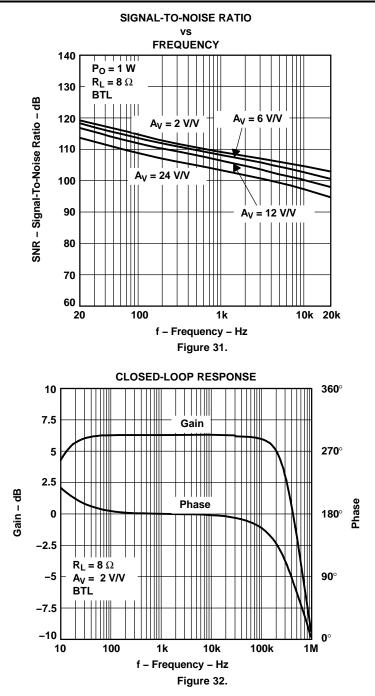

| SNR            | Signal-to-noise ratio                | vs Frequency           | 31                            |

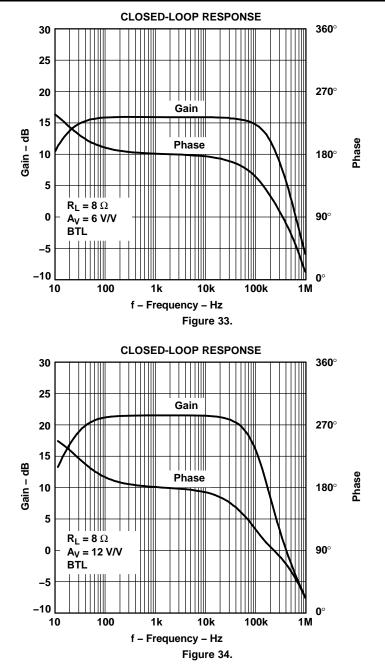

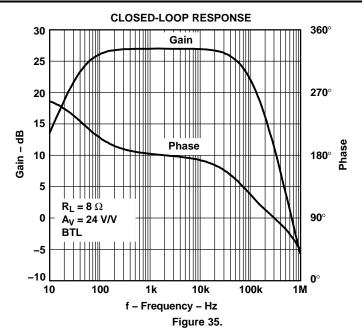

|                | Closed-loop respone                  |                        | 32-35                         |

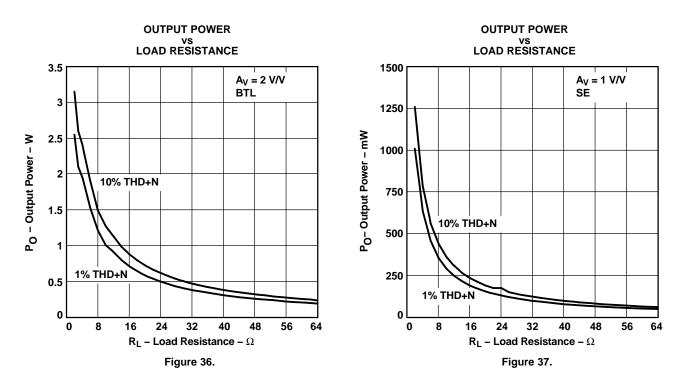

| Po             | Output power                         | vs Load resistance     | 36, 37                        |

| <b>D</b>       | Device disainstice                   | vs Output power        | 38, 39                        |

| P <sub>D</sub> | Power dissipation                    | vs Ambient temperature | 40                            |

+ + + + + + + f = 15 kHz f = 1 kHz $\pm$ f = 20 Hz  $R_L = 3 \Omega$  $A_V = 2 V/V$ BTL 0.01 0.1 1 10 Po - Output Power - W

TOTAL HARMONIC DISTORTION PLUS NOISE vs OUTPUT POWER

TOTAL HARMONIC DISTORTION PLUS NOISE vs OUTPUT POWER

f = 15 kHz

f = 1 kHz

f = 20 Hz

Figure 12.

vs FREQUENCY

$P_{O} = 0.5 W$

Figure 14.

1k

1

P<sub>O</sub> = 1.0 W

10k 20k

10

10

SLOS204C-MAY 1999-REVISED SEPTEMBER 2004

1

1

#### TOTAL HARMONIC DISTORTION PLUS NOISE vs OUTPUT POWER

10

1**0**%

1%

0.1%

0.01%

0.01

THD+N – Total Harmonic Distortion + Noise

0.1

$R_L = 8 \Omega$  $A_V = 24 V/V$

BŤL

TOTAL HARMONIC DISTORTION PLUS NOISE

vs OUTPUT POWER

f = 15 kHz

f = 1 kHz

f = 20 Hz

1

10

TOTAL HARMONIC DISTORTION PLUS NOISE

Po - Output Power - W

Figure 19.

TOTAL HARMONIC DISTORTION PLUS NOISE vs FREQUENCY

10

Figure 26.

Figure 40.

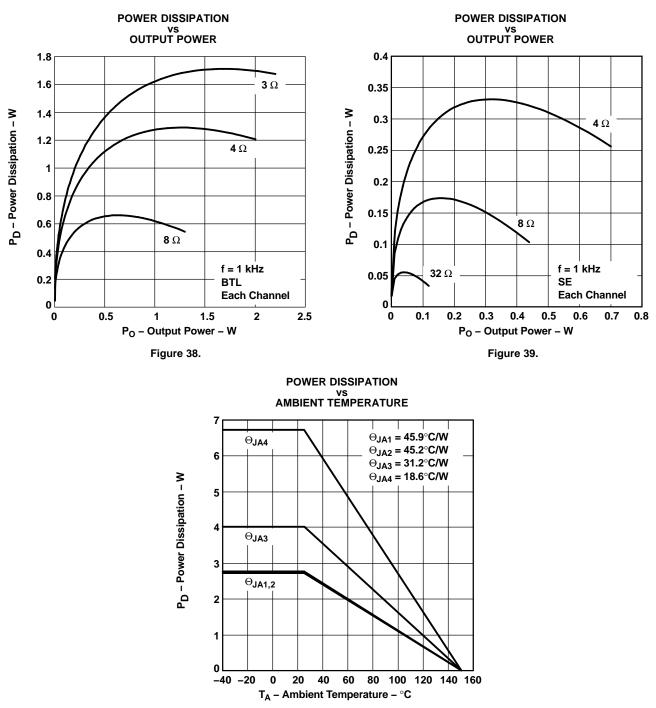

#### THERMAL INFORMATION

The thermally enhanced PWP package is based on the 24-pin TSSOP, but includes a thermal pad (see Figure 41) to provide an effective thermal contact between the IC and the PWB.

Traditionally, surface mount and power have been mutually exclusive terms. A variety of scaled-down TO-220-type packages have leads formed as gull wings to make them applicable for surface-mount applications. These packages, however, have only two shortcomings: they do not address the low-profile requirements (< 2 mm) of many of today's advanced systems, and they do not offer a terminal-count high enough to accommodate increasing integration. On the other hand, traditional low-power surface-mount packages require power-dissipation derating that severely limits the usable range of many high-performance analog circuits.

The PowerPAD package (thermally enhanced TSSOP) combines fine-pitch surface-mount technology with thermal performance comparable to much larger power packages.

The PowerPAD package is designed to optimize the heat transfer to the PWB. Because of the small size and limited mass of a TSSOP package, thermal enhancement is achieved by improving the thermal conduction paths that remove heat from the component. The thermal pad is formed using a patented lead-frame design and manufacturing technique to provide a direct connection to the heat-generating IC. When this pad is soldered or otherwise thermally coupled to an external heat dissipator, high power dissipation in the ultra-thin, fine-pitch, surface-mount package can be reliably achieved.

Bottom View (c)

Figure 41. Views of Thermally Enhanced PWP Package

### **APPLICATION INFORMATION**

### **SELECTION OF COMPONENTS**

Figure 42 and Figure 43 are schematic diagrams of typical notebook computer application circuits.

Figure 42. Typical TPA0112 Application Circuit Using Single-Ended Inputs and Input MUX

#### **APPLICATION INFORMATION (continued)**

A. A 0.1-μF ceramic capacitor should be placed as close as possible to the IC. For filtering lower frequency noise signals, a larger electrolytic capacitor of 10 μF or greater should be placed near the audio power amplifier.

Figure 43. Typical TPA0112 Application Circuit Using Differential Inputs

# APPLICATION INFORMATION (continued)

## GAIN-SETTING VIA GAIN0 AND GAIN1 INPUTS

The gain of the TPA0112 is set by two input terminals, GAIN0 and GAIN1.

| GAIN0 | GAIN1 | SE/BTL | Av     |

|-------|-------|--------|--------|

| 0     | 0     | 0      | 2 V/V  |

| 0     | 1     | 0      | 6 V/V  |

| 1     | 0     | 0      | 12 V/V |

| 1     | 1     | 0      | 24 V/V |

| Х     | Х     | 1      | 1 V/V  |

#### Table 1. GAIN SETTINGS

The gains listed in Table 1 are realized by changing the taps on the input resistors inside the amplifier. This causes the input impedance,  $Z_1$ , to be dependent on the gain setting. The actual gain settings are controlled by ratios of resistors, so the actual gain distribution from part-to-part is quite good. However, the input impedance will shift by 30% due to shifts in the actual resistance of the input impedance.

For design purposes, the input network (discussed in the next section) should be designed assuming an input impedance of 10 k $\Omega$ , which is the absolute minimum input impedance of the TPA0112. At the higher gain settings, the input impedance could increase as high as 115 k $\Omega$ .

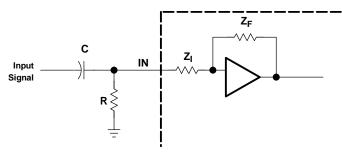

#### INPUT RESISTANCE

Each gain setting is achieved by varying the input resistance of the amplifier, which can range from its smallest value to over 6 times that value. As a result, if a single capacitor is used in the input high-pass filter, the -3 dB or cutoff frequency also changes by over 6 times. If an additional resistor is connected from the input pin of the amplifier to ground, as shown in the following figure, the variation of the cutoff frequency will be much reduced.

The input impedance at each gain setting is given in the following table:

| Av     | ZI      |

|--------|---------|

| 24 V/V | 14 kΩ   |

| 12 V/V | 26 kΩ   |

| 6 V/V  | 45.5 kΩ |

| 2 V/V  | 91 kΩ   |

The –3 dB frequency can be calculated using Equation 1:

$$f_{-3 dB} = \frac{1}{2\pi C(R \parallel R_{I})}$$

(1)

If the filter must be more accurate, the value of the capacitor should be increased while the value of the resistor to ground should be decreased. In addition, the order of the filter could be increased.

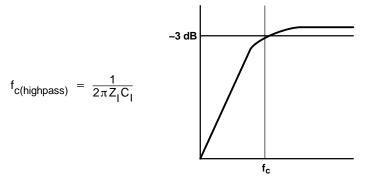

### INPUT CAPACITOR, C<sub>I</sub>

In the typical application, an input capacitor,  $C_I$ , is required to allow the amplifier to bias the input signal to the proper dc level for optimum operation. In this case,  $C_I$  and the input impedance of the amplifier,  $Z_I$ , form a high-pass filter with the corner frequency determined in Equation 2.

(2)

The value of C<sub>1</sub> is important to consider as it directly affects the bass (low-frequency) performance of the circuit. Consider the example where Z<sub>1</sub> is 26 k $\Omega$  and the specification calls for a flat bass response down to 65 Hz. Equation 2 is reconfigured as Equation 3.

$$C_{I} = \frac{1}{2\pi Z_{I} f_{c}}$$

<sup>(3)</sup>

In this example,  $C_1$  is 94 nF so one would likely choose a value in the range of 0.1  $\mu$ F to 1  $\mu$ F. A further consideration for this capacitor is the leakage path from the input source through the input network ( $C_1$ ) and the feedback network to the load. This leakage current creates a dc-offset voltage at the input to the amplifier that reduces useful headroom, especially in high gain applications. For this reason a low-leakage tantalum or ceramic capacitor is the best choice. When polarized capacitors are used, the positive side of the capacitor should face the amplifier input in most applications as the dc level there is held at  $V_{DD}/2$ , which is likely higher than the source dc level. Note that it is important to confirm the capacitor polarity in the application.

#### POWER SUPPLY DECOUPLING, Cs

The TPA0112 is a high-performance CMOS audio amplifier that requires adequate power supply decoupling to ensure that the output total harmonic distortion (THD) is as low as possible. Power supply decoupling also prevents oscillations for long lead lengths between the amplifier and the speaker. The optimum decoupling is achieved by using two capacitors of different types that target different types of noise on the power supply leads. For higher frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically 0.1  $\mu$ F placed as close as possible to the device V<sub>DD</sub> lead works best. For filtering lower frequency noise signals, a larger aluminum electrolytic capacitor of 10  $\mu$ F or greater placed near the audio power amplifier is recommended.

#### MIDRAIL BYPASS CAPACITOR, CBYP

The midrail bypass capacitor,  $C_{BYP}$ , is the most critical capacitor and serves several important functions. During start-up or recovery from shutdown mode,  $C_{BYP}$  determines the rate at which the amplifier starts up. The second function is to reduce noise produced by the power supply caused by coupling into the output drive signal. This noise is from the midrail generation circuit internal to the amplifier, which appears as degraded PSRR and THD+N.

Bypass capacitor,  $C_{BYP}$ , values of 0.47- $\mu$ F to 1- $\mu$ F ceramic or tantalum low-ESR capacitors are recommended for the best THD and noise performance.

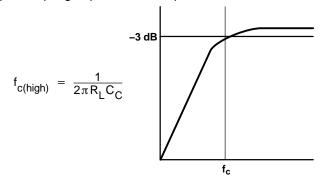

#### OUTPUT COUPLING CAPACITOR, C<sub>c</sub>

In the typical single-supply, SE configuration, an output coupling capacitor ( $C_c$ ) is required to block the dc bias at the output of the amplifier, thus preventing dc currents in the load. As with the input coupling capacitor, the output coupling capacitor and impedance of the load form a high-pass filter governed by Equation 4.

(4)

The main disadvantage, from a performance standpoint, is the load impedances are typically small, which drives the low-frequency corner higher degrading the bass response. Large values of C<sub>C</sub> are required to pass low frequencies into the load. Consider the example where a C<sub>C</sub> of 330  $\mu$ F is chosen and loads vary from 3  $\Omega$ , 4  $\Omega$ , 8  $\Omega$ , 32  $\Omega$ , 10 k $\Omega$ , to 47 k $\Omega$ . Table 2 summarizes the frequency response characteristics of each configuration.

| Table 2. COMMON-LOAD IMPEDANCES Vs LOW-FREQUENCY OUTPUT |

|---------------------------------------------------------|

| CHARACTERISTICS IN SE MODE                              |

| RL       | Cc     | LOWEST FREQUENCY |

|----------|--------|------------------|

| 3 Ω      | 330 µF | 161 Hz           |

| 4 Ω      | 330 µF | 120 Hz           |

| 8 Ω      | 330 µF | 60 Hz            |

| 32 Ω     | 330 µF | 15 Hz            |

| 10,000 Ω | 330 µF | 0.05 Hz          |

| 47,000 Ω | 330 µF | 0.01 Hz          |

As Table 2 indicates, most of the bass response is attenuated into a  $4-\Omega$  load, an  $8-\Omega$  load is adequate, headphone response is good, and drive into line-level inputs (a home stereo for example) is exceptional.

#### **USING LOW-ESR CAPACITORS**

Low-ESR capacitors are recommended throughout this applications section. A real (as opposed to ideal) capacitor can be modeled simply as a resistor in series with an ideal capacitor. The voltage drop across this resistor minimizes the beneficial effects of the capacitor in the circuit. The lower the equivalent value of this resistance the more the real capacitor behaves like an ideal capacitor.

#### BRIDGE-TIED LOAD VERSUS SINGLE-ENDED MODE

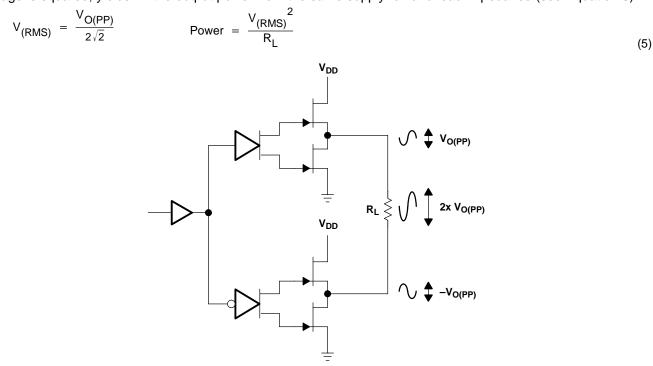

Figure 44 shows a Class-AB audio power amplifier (APA) in a BTL configuration. The TPA0112 BTL amplifier consists of two Class-AB amplifiers driving both ends of the load. There are several potential benefits to this differential drive configuration but initially consider power to the load. The differential drive to the speaker means that as one side is slewing up, the other side is slewing down, and vice versa. This, in effect, doubles the voltage swing on the load as compared to a ground-referenced load. Plugging  $2 \times V_{O(PP)}$  into the power equation, where voltage is squared, yields  $4\times$  the output power from the same supply rail and load impedance (see Equation 5).

Figure 44. Bridge-Tied Load Configuration

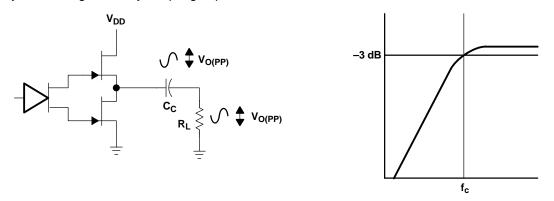

In a typical computer sound channel operating at 5 V, bridging raises the power into an 8- $\Omega$  speaker from a singled-ended (SE, ground reference) limit of 250 mW to 1 W. In sound power, that is a 6-dB improvement—which is loudness that can be heard. In addition to increased power there are frequency response concerns. Consider the single-supply, SE configuration shown in Figure 45. A coupling capacitor is required to block the dc-offset voltage from reaching the load. These capacitors can be quite large (approximately 33  $\mu$ F to 1000  $\mu$ F); so they tend to be expensive, heavy, occupy valuable PCB area, and have the additional drawback of limiting low-frequency performance of the system. This frequency-limiting effect is due to the high-pass filter network created with the speaker impedance and the coupling capacitance and is calculated with Equation 6.

$$f_{\rm C} = \frac{1}{2\pi R_{\rm L} C_{\rm C}} \tag{6}$$

For example, a  $68-\mu$ F capacitor with an  $8-\Omega$  speaker would attenuate low frequencies below 293 Hz. The BTL configuration cancels the dc offsets, which eliminates the need for the blocking capacitors. Low-frequency performance is then limited only by the input network and speaker response. Cost and PCB space are also minimized by eliminating the bulky coupling capacitor.

Figure 45. Single-Ended Configuration and Frequency Response

Increasing power to the load does carry a penalty of increased internal power dissipation. The increased dissipation is understandable considering that the BTL configuration produces 4× the output power of the SE configuration. Internal dissipation versus output power is discussed further in the *Crest Factor and Thermal Considerations* section.

#### SINGLE-ENDED OPERATION

In SE mode (see Figure 44 and Figure 45), the load is driven from the primary amplifier output for each channel (OUT+, terminals 21 and 4).

The amplifier switches single-ended operation when the SE/BTL terminal is held high. This puts the negative outputs in a high-impedance state and reduces the amplifier's gain to 1 V/V.

#### **BTL AMPLIFIER EFFICIENCY**

Class-AB amplifiers are notoriously inefficient. The primary cause of these inefficiencies is voltage drop across the output stage transistors. There are two components of the internal voltage drop. One is the headroom or dc voltage drop that varies inversely to output power. The second component is due to the sine-wave nature of the output. The total voltage drop can be calculated by subtracting the RMS value of the output voltage from  $V_{DD}$ . The internal voltage drop multiplied by the RMS value of the supply current,  $I_{DD}$ rms, determines the internal power dissipation of the amplifier.

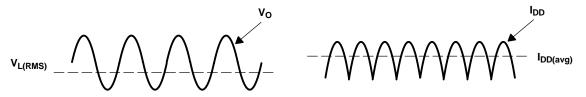

An easy-to-use equation to calculate efficiency starts out as being equal to the ratio of power from the power supply to the power delivered to the load. To accurately calculate the RMS and average values of power in the load and in the amplifier, the current and voltage waveform shapes must first be understood (see Figure 46).

Figure 46. Voltage and Current Waveforms for BTL Amplifiers

Although the voltages and currents for SE and BTL are sinusoidal in the load, currents from the supply are different between SE and BTL configurations. In an SE application the current waveform is a half-wave rectified shape, whereas in BTL it is a full-wave rectified waveform. This means RMS conversion factors are different. Keep in mind that for most of the waveform, both the push and pull transistors are not on at the same time, which supports the fact that each amplifier in the BTL device only draws current from the supply for half the waveform. The following equations are the basis for calculating amplifier efficiency.

Efficiency of a BTL amplifier =

$$\frac{P_L}{P_{SUF}}$$

Where:

$$P_{L} = \frac{V_{L(RMS)}^{2}}{R_{I}}$$

, and  $V_{L(RMS)} = \frac{V_{P}}{\sqrt{2}}$ , therefore,  $P_{L} = \frac{V_{P}^{2}}{2R_{I}}$

and  $P_{SUP} = V_{DD} I_{DD(avg)}$  and  $I_{DD(avg)} = \frac{1}{\pi} \int_0^{\pi} \frac{V_P}{R_L} \sin(t) dt = -\frac{1}{\pi} \times \frac{V_P}{R_L} [\cos(t)]_0^{\pi} = \frac{2V_P}{\pi R_L}$

Therefore,

$$\mathsf{P}_{\mathsf{SUP}} = \frac{2\,\mathsf{V}_{\mathsf{DD}}\,\mathsf{V}_{\mathsf{F}}}{\pi\,\mathsf{R}_{\mathsf{L}}}$$

substituting PL and PSUP into Equation 7,

Efficiency of a BTL amplifier

$$= \frac{\frac{V_P^2}{2R_L}}{\frac{2V_{DD}V_P}{\pi R_L}} = \frac{\pi V_P}{4V_{DD}}$$

Where:

$$V_{P} = \sqrt{2 P_{L} R_{L}}$$

$\begin{array}{l} \mathsf{P}_{\mathsf{L}} = \mathsf{Power} \ \mathsf{delivered} \ \mathsf{to} \ \mathsf{load} \\ \mathsf{P}_{\mathsf{SUP}} = \mathsf{Power} \ \mathsf{drawn} \ \mathsf{from} \ \mathsf{power} \ \mathsf{supply} \\ \mathsf{V}_{\mathsf{L}(\mathsf{RMS})} = \mathsf{RMS} \ \mathsf{voltage} \ \mathsf{on} \ \mathsf{BTL} \ \mathsf{load} \\ \mathsf{R}_{\mathsf{L}} = \mathsf{Load} \ \mathsf{resistance} \\ \mathsf{V}_{\mathsf{P}} = \mathsf{Peak} \ \mathsf{voltage} \ \mathsf{on} \ \mathsf{BTL} \ \mathsf{load} \\ \mathsf{I}_{\mathsf{DD}}(\mathsf{avg}) = \mathsf{Average} \ \mathsf{current} \ \mathsf{drawn} \ \mathsf{from} \\ \mathsf{the} \ \mathsf{power} \ \mathsf{supply} \\ \mathsf{V}_{\mathsf{DD}} = \mathsf{Power} \ \mathsf{supply} \ \mathsf{voltage} \\ \mathfrak{\eta}_{\mathsf{BTL}} = \mathsf{Efficiency} \ \mathsf{of} \ \mathsf{a} \ \mathsf{BTL} \ \mathsf{amplifier} \end{array}$

Therefore,

$$\eta_{\text{BTL}} = \frac{\pi \sqrt{2 \,\text{P}_{\text{L}} \text{R}_{\text{L}}}}{4 \,\text{V}_{\text{DD}}}$$

(8)

(7)

Table 3 employs Equation 8 to calculate efficiencies for four different output power levels. Note that the efficiency of the amplifier is quite low for lower power levels and rises sharply as power to the load is increased, resulting in a nearly flat internal power dissipation over the normal operating range. Note that the internal dissipation at full output power is less than in the half power range. Calculating the efficiency for a specific system is the key to proper power supply design. For a stereo 1-W audio system with 8- $\Omega$  loads and a 5-V supply, the maximum draw on the power supply is almost 3.25 W.

#### Table 3. EFFICIENCY Vs OUTPUT POWER IN 5-V, 8-Ω, BTL SYSTEMS

| OUTPUT POWER<br>(W) | EFFICIENCY<br>(%) | PEAK VOLTAGE<br>(V) | INTERNAL DISSIPATION<br>(W) |

|---------------------|-------------------|---------------------|-----------------------------|

| 0.25                | 31.4              | 2.00                | 0.55                        |

| 0.50                | 44.4              | 2.83                | 0.62                        |

| 1.00                | 62.8              | 4.00                | 0.59                        |

| 1.25                | 70.2              | 4.47 <sup>(1)</sup> | 0.53                        |

(1) High peak voltages cause the THD to increase.

A final point to remember about Class-AB amplifiers (either SE or BTL) is how to manipulate the terms in the efficiency equation to utmost advantage when possible. Note that in Equation 8,  $V_{DD}$  is in the denominator. This indicates that as  $V_{DD}$  goes down, efficiency goes up.

#### **CREST FACTOR AND THERMAL CONDITIONS**

Class-AB power amplifiers dissipate a significant amount of heat in the package under normal operating conditions. A typical music CD requires 12 dB to 15 dB of dynamic range, or headroom above the average power output, to pass the loudest portions of the signal without distortion. In other words, music typically has a crest factor between 12 dB and 15 dB. When determining the optimal ambient operating temperature, the internal dissipated power at the average output power level must be used. From the TPA0112 data sheet, one can see that when the TPA0112 is operating from a 5-V supply into a  $3-\Omega$  speaker that 4-W peaks are available. Converting watts to dB:

$$P_{dB} = 10 \log \frac{P_W}{P_{ref}} = 10 \log \frac{4 W}{1 W} = 6 dB$$

(9)

Subtracting the headroom restriction to obtain the average listening level without distortion yields:

6 dB - 15 dB = - 9 dB (15-dB crest factor) 6 dB - 12 dB = - 6 dB (12-dB crest factor) 6 dB - 9 dB = - 3 dB (9-dB crest factor) 6 dB - 6 dB = 0 dB (6-dB crest factor) 6 dB - 3 dB = 3 dB (3-dB crest factor)

Converting dB back into watts:

$$P_W = 10^{PdB/10} \times P_{ref}$$

- = 63 mW (18–dB crest factor)

- = 125 mW (15-dB crest factor)

- = 250 mW (9–dB crest factor)

- = 500 mW (6-dB crest factor)

- = 1000 mW (3–dB crest factor)

- = 2000 mW (15-dB crest factor)

This is valuable information to consider when attempting to estimate the heat dissipation requirements for the amplifier system. Comparing the absolute worst case, which is 2 W of continuous power output with a 3-dB crest factor, against 12-dB and 15-dB applications drastically affects maximum ambient temperature ratings for the system. Using the power dissipation curves for a 5-V,  $3-\Omega$  system, the internal dissipation in the TPA0112 and maximum ambient temperatures is shown in Table 4.

| PEAK OUTPUT POWER<br>(W) | AVERAGE OUTPUT POWER | POWER DISSIPATION<br>(W/Channel) | MAXIMUM AMBIENT<br>TEMPERATURE <sup>(1)</sup> |

|--------------------------|----------------------|----------------------------------|-----------------------------------------------|

| 4                        | 2 W (3 dB)           | 1.7                              | -3°C                                          |

| 4                        | 1000 mW (6 dB)       | 1.6                              | 6°C                                           |

| 4                        | 500 mW (9 dB)        | 1.4                              | 24°C                                          |

| 4                        | 250 mW (12 dB)       | 1.1                              | 51°C                                          |

| 4                        | 125 mW (15 dB)       | 0.8                              | 78°C                                          |

| 4                        | 63 mW (18 dB)        | 0.6                              | 85°C                                          |

#### Table 4. TPA0112 POWER RATING, 5-V, 3-Ω, STEREO

(1) Package limited to85°C ambient.

(9)

(10)

| PEAK OUTPUT POWER | AVERAGE OUTPUT POWER        | POWER DISSIPATION<br>(W/Channel) | MAXIMUM AMBIENT<br>TEMPERATURE <sup>(1)</sup> |  |  |  |  |  |  |

|-------------------|-----------------------------|----------------------------------|-----------------------------------------------|--|--|--|--|--|--|

| 2.5 W             | 1250 mW (3-dB crest factor) | 0.55                             | 85°C                                          |  |  |  |  |  |  |

| 2.5 W             | 1000 mW (4-dB crest factor) | 0.62                             | 85°C                                          |  |  |  |  |  |  |

| 2.5 W             | 500 mW (7-dB crest factor)  | 0.59                             | 85°C                                          |  |  |  |  |  |  |

| 2.5 W             | 250 mW (10-dB crest factor) | 0.53                             | 85°C                                          |  |  |  |  |  |  |

Table 5. TPA0112 POWER RATING, 5-V, 8-Ω, STEREO

(1) Package limited to85°C ambient.

The maximum dissipated power,  $P_{Dmax}$ , is reached at a much lower output power level for a 3- $\Omega$  load than for an 8- $\Omega$  load. As a result, this simple formula for calculating  $P_{D(max)}$  may be used for a 3- $\Omega$  application:

$$\mathsf{P}_{\mathsf{D}(\mathsf{max})} = \frac{2\mathsf{V}_{\mathsf{D}\mathsf{D}}^2}{\pi^2\mathsf{R}_{\mathsf{L}}} \tag{11}$$

However, in the case of an 8- $\Omega$  load, the P<sub>D(max)</sub> occurs at a point well above the normal operating power level. The amplifier may therefore be operated at a higher ambient temperature than required by the P<sub>D(max)</sub> formula for an 8- $\Omega$  load, but do not exceed the maximum ambient temperature of 85°C.

The maximum ambient temperature depends on the heat-sinking ability of the PCB system. The derating factor for the PWP package is shown in the dissipation rating table (see page 4). Converting this to  $\theta_{JA}$ :

$$\Theta_{JA} = \frac{1}{\text{Derating Factor}} = \frac{1}{0.022} = 45^{\circ}\text{C/W}$$

(12)

To calculate maximum ambient temperatures, first consider that the numbers from the dissipation graphs are per channel so the dissipated power needs to be doubled for two-channel operation. Given  $\theta_{JA}$ , the maximum allowable junction temperature, and the total internal dissipation, the maximum ambient temperature can be calculated with the following equation. The maximum recommended junction temperature for the TPA0112 is 150°C. The internal dissipation figures are taken from the Power Dissipation vs Output Power graphs.

$$T_{A} Max = T_{J} Max - \Theta_{JA} P_{D}$$

= 150 - 45(0.6 × 2) = 96°C (15-dB crest factor) (13)

A. Internal dissipation of 0.6 W is estimated for a 2-W system with 15-dB crest factor per channel. Due to process limitations, the actual T<sub>A</sub> Max is 85°C.

Tables 4 and 5 show that for some applications no airflow is required to keep junction temperatures in the specified range. The TPA0112 is designed with thermal protection that turns the device off when the junction temperature surpasses 150°C to prevent damage to the IC. Tables 4 and 5 were calculated for maximum listening volume without distortion. When the output level is reduced, the numbers in the table change significantly. Also, using 8- $\Omega$  speakers dramatically increases the thermal performance by increasing amplifier efficiency.

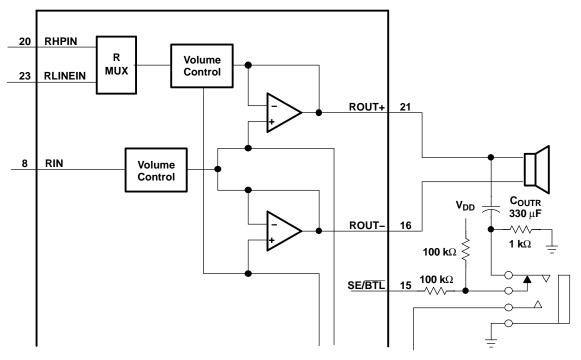

## SE/BTL OPERATION

The ability of the TPA0112 to easily switch between BTL and SE modes is one of its most important cost-saving features. This feature eliminates the requirement for an additional headphone amplifier in applications where internal stereo speakers are driven in BTL mode but external headphone or speakers must be accommodated. Internal to the TPA0112, two separate amplifiers drive OUT+ and OUT-. The SE/BTL input (terminal 15) controls the operation of the follower amplifier that drives LOUT- and ROUT- (terminals 9 and 16). When SE/BTL is held low, the amplifier is on and the TPA0112 is in the BTL mode. When SE/BTL is held high, the OUT- amplifiers are in a high output impedance state, which configures the TPA0112 as an SE driver from LOUT+ and ROUT+ (terminals 4 and 21). I<sub>DD</sub> is reduced by approximately one-half in SE mode. Control of the SE/BTL input can be from a logic-level CMOS source or, more typically, from a resistor divider network as shown in Figure 47.

Figure 47. TPA0112 Resistor Divider Network Circuit

Using a readily available 1/8-in. (3,5-mm) stereo headphone jack, the control switch is closed when no plug is inserted. When closed, the 100-k $\Omega$ /1-k $\Omega$  divider pulls the SE/BTL input low. When a plug is inserted, the 1-k $\Omega$  resistor is disconnected and the SE/BTL input is pulled high. When the input goes high, the OUT– amplifier is shut down causing the speaker to mute (virtually open-circuits the speaker). The OUT+ amplifier then drives through the output capacitor (C<sub>O</sub>) into the headphone jack.

#### PC-BEEP OPERATION

The PC-BEEP input allows a system beep to be sent directly from a computer through the amplifier to the speakers with few external components. The input is normally activated automatically, but may be selected manually by pulling PCB ENABLE high. When the PC-BEEP input is active, both of the LINEIN and HPIN inputs are deselected and both the left and right channels are driven in BTL mode with the signal from PC-BEEP. The gain from the PC-BEEP input to the speakers is fixed at 0.3 V/V and is independent of the volume setting. When the PC-BEEP input is deselected, the amplifier returns to the previous operating mode and volume setting. Furthermore, if the amplifier is in shutdown mode, activating PC-BEEP takes the device out of shutdown and outputs the PC-BEEP signal, then returns the amplifier to shutdown mode.

When PCB ENABLE is held low, the amplifier automatically switches to PC BEEP mode after detecting a valid signal at the PC BEEP input. The preferred input signal is a square wave or pulse train with an amplitude of 1.5  $V_{pp}$  or greater. To be a accurately detected, the signal must have a minimum of  $1.5 \cdot V_{pp}$  amplitude, rise and fall times of less than 0.1 µs and a minimum of 8 rising edges. When the signal is no longer detected, the amplifier returns to its previous operating mode and volume setting.

When PCB ENABLE is held high, PC BEEP is selected and the LINEIN and HPIN inputs are deactivated regardless of the input signal. PCB ENABLE has an internal 100-k $\Omega$  pulldown resistor and trips at approximately V<sub>DD</sub>/2.

If it is desired to ac-couple the PC-BEEP input, the value of the coupling capacitor should be chosen to satisfy Equation 14:

$$C_{\text{PCB}} \ge \frac{1}{2\pi f_{\text{PCB}} (100 \text{ k}\Omega)}$$

(14)

The PC BEEP input can also be dc-coupled to avoid using this coupling capacitor. The pin normally sits at midrail when no signal is present.

#### INPUT MUX OPERATION

Figure 48. TPA0112 Example Input MUX Circuit

The input MUX provides the user with a means to select from two different audio sources. In BTL mode, the LINE inputs are selected. In SE mode, the HP inputs are selected.  $R_{IN}$  and  $L_{IN}$  must be ac grounded in SE mode.

#### SHUTDOWN MODES

The TPA0112 employs a shutdown mode of operation designed to reduce supply current,  $I_{DD}$ , to the absolute minimum level during periods of nonuse for battery-power conservation. The <u>SHUTDOWN</u> input terminal should be held high during normal operation when the amplifier is in use. Pulling <u>SHUTDOWN</u> low causes the outputs to mute and the amplifier to enter a low-current state,  $I_{DD} = 150 \ \mu A$ . SHUTDOWN should never be left unconnected because amplifier operation would be unpredictable.

| INP              | UTS <sup>(1)</sup> | AMPLIFIER STATE  |        |  |

|------------------|--------------------|------------------|--------|--|

| SE/BTL           | SHUTDOWN           | INPUT            | OUTPUT |  |

| Low              | High               | Line             | BTL    |  |

| X <sup>(2)</sup> | Low                | X <sup>(2)</sup> | Mute   |  |

| High             | High               | HP               | SE     |  |

(2) Stresses beyond thoselisted under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at theseor any other conditions beyond those indicated under recommended operatingconditions is not implied. Exposure to absolute-maximum-rated conditions forextended periods may affect device reliability.

<sup>(1)</sup> Inputs should never be leftunconnected.

#### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup>  | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|----------------------------|------------------|------------------------------|

| TPA0112PWP       | ACTIVE                | HTSSOP          | PWP                | 24   | 60             | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPA0112PWPG4     | ACTIVE                | HTSSOP          | PWP                | 24   | 60             | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPA0112PWPR      | ACTIVE                | HTSSOP          | PWP                | 24   | 2000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPA0112PWPRG4    | ACTIVE                | HTSSOP          | PWP                | 24   | 2000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

TEXAS INSTRUMENTS www.ti.com

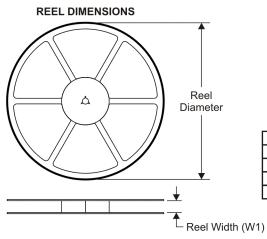

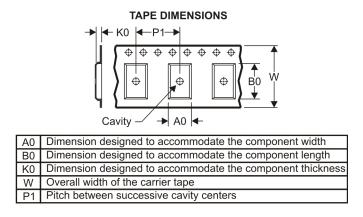

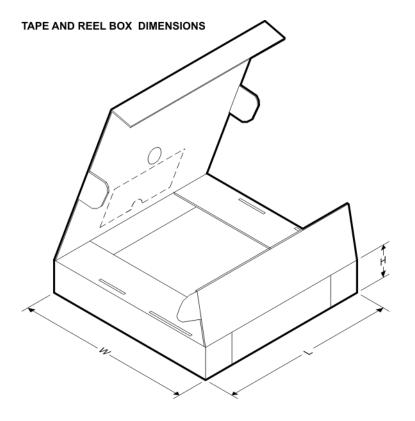

### TAPE AND REEL INFORMATION

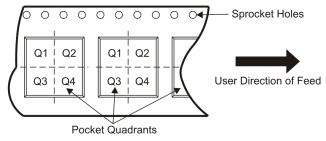

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions a | are nominal |

|-------------------|-------------|

|-------------------|-------------|

| Device      | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| TPA0112PWPR | HTSSOP          | PWP                | 24 | 2000 | 330.0                    | 16.4                     | 6.95    | 8.3     | 1.6     | 8.0        | 16.0      | Q1               |

# PACKAGE MATERIALS INFORMATION

11-Mar-2008

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPA0112PWPR | HTSSOP       | PWP             | 24   | 2000 | 346.0       | 346.0      | 33.0        |

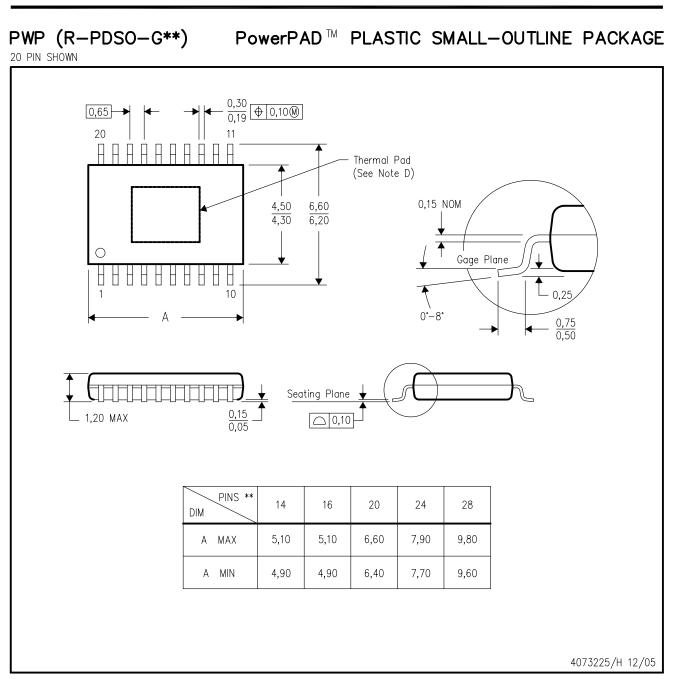

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

#### THERMAL INFORMATION

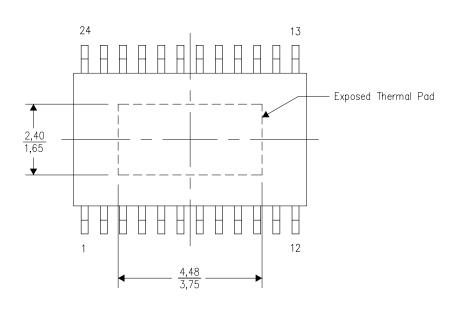

This PowerPAD<sup>™</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

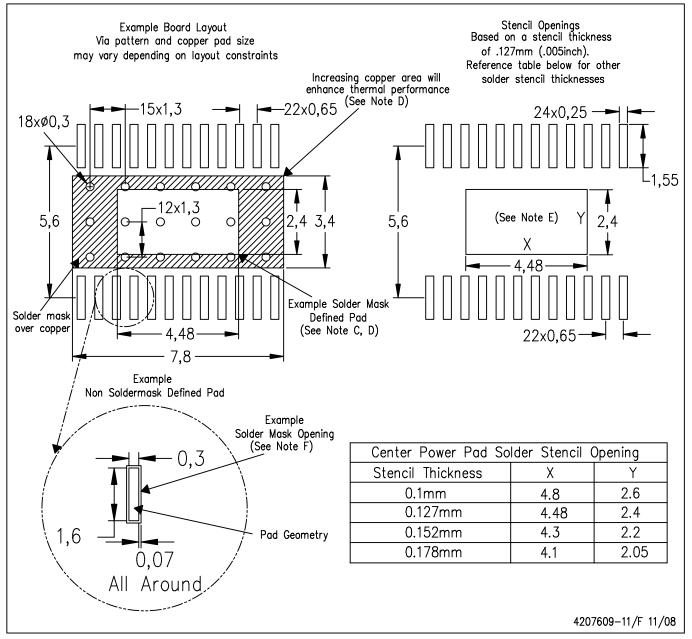

# LAND PATTERN

# PWP (R-PDSO-G24) PowerPAD™

NOTES:

- A. All linear dimensions are in millimeters.B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <http://www.ti.com>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads. PowerPAD is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                         | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Clocks and Timers           | www.ti.com/clocks      | Digital Control    | www.ti.com/digitalcontrol |

| Interface                   | interface.ti.com       | Medical            | www.ti.com/medical        |

| Logic                       | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt                  | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers            | microcontroller.ti.com | Security           | www.ti.com/security       |

| RFID                        | www.ti-rfid.com        | Telephony          | www.ti.com/telephony      |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video & Imaging    | www.ti.com/video          |

|                             |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated